**TANDY®**

# Service Manual

# PORTABLE DISK DRIVE 2

Catalog Number: 26-3814

CUSTOM MANUFACTURED FOR RADIO SHACK, A DIVISION OF TANDY CORPORATION

# Portable Disk Drive 2 Service Manual

Copyright 1987 Tandy Corporation.

All Rights Reserved.

Tandy is a registered trademark of Tandy Corporation.

Reproduction or use without express written permission from Tandy Corporation, of any portion of this manual is prohibited. While reasonable efforts have been taken in the preparation of this manual to assure its accuracy, Tandy Corporation assumes no liability resulting from errors in or omissions from this manual, or from the use of the information contained herein.

10 9 8 7 6 5 4 3 2 1

# **Table of Contents**

| 1.  |                                           |          |    |  |  |  |

|-----|-------------------------------------------|----------|----|--|--|--|

| 2.  | GENERAL SPECIFICATIONS                    | •••      | 2  |  |  |  |

| 3.  | DISASSEMBLY INSTRUCTIONS                  |          |    |  |  |  |

|     | 3-1. Disassembly ·····                    |          |    |  |  |  |

|     | 3-2. Reassembly ·····                     |          |    |  |  |  |

| 4.  | BLOCK DIAGRAM                             |          |    |  |  |  |

| 5.  | PRINCIPLES OF MECHANICAL OPERATION        |          |    |  |  |  |

|     | 5-1. Structure of Disk ·····              | ′        | 10 |  |  |  |

|     | 5-2. Disk Driving Mechanism               | ·        | 11 |  |  |  |

|     | 5-3. Head Positioning Mechanism           | ·        | 11 |  |  |  |

|     | 5-4. Structure of Read/Write Head ·····   | <i>'</i> | 12 |  |  |  |

|     | 5-5. Pad Mechanism ·····                  | <i>'</i> | 12 |  |  |  |

|     | 5-6. Disk Eject Mechanism                 | ·        | 13 |  |  |  |

|     | 5-7. Write Protector                      | ·        | 13 |  |  |  |

|     | 5-8. Index                                |          | 13 |  |  |  |

|     | 5-9. Disk Detection                       | '        | 13 |  |  |  |

|     | 5-10. Home Position Return ·····          | ٠        | 14 |  |  |  |

| 6.  | PRINCIPLES OF ELECTRONIC OPERATION        |          | 15 |  |  |  |

|     | 6-1. Electronic Components ·····          | '        | 15 |  |  |  |

|     | 6-2. Main PCB                             |          |    |  |  |  |

|     | 6-3. Panel PCB ·····                      | ;        | 32 |  |  |  |

|     | 6-4. Power PCB                            | ;        | 33 |  |  |  |

| 7.  | EXPLANATION OF BASIC OPERATION            | ;        | 34 |  |  |  |

|     | 7-1. Power On/Reset Operation             | ;        | 34 |  |  |  |

|     | 7-2. Track 0 Operation ·····              |          |    |  |  |  |

|     | 7-3. Seek Operation                       | ;        | 36 |  |  |  |

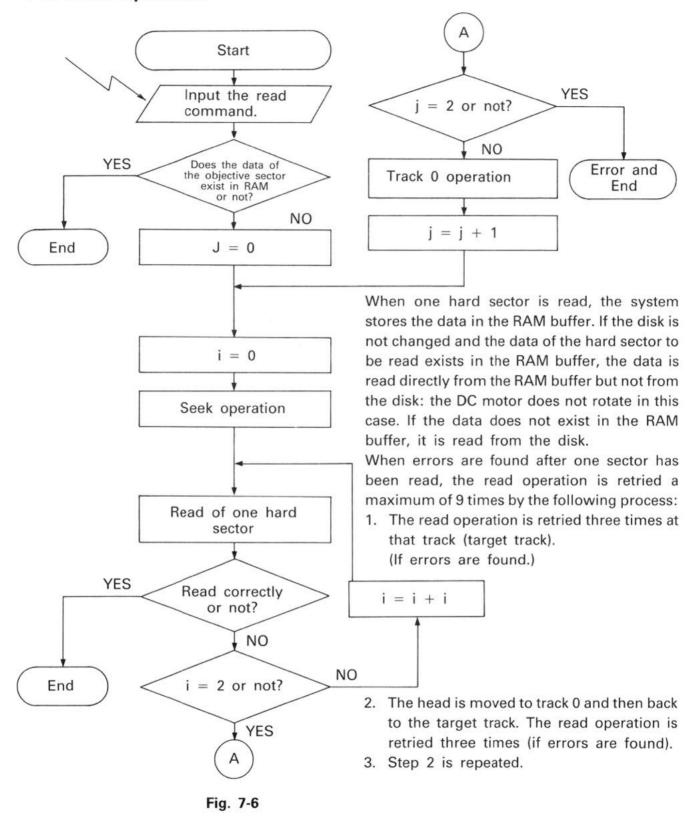

|     | 7-4. Read Operation                       | ;        | 38 |  |  |  |

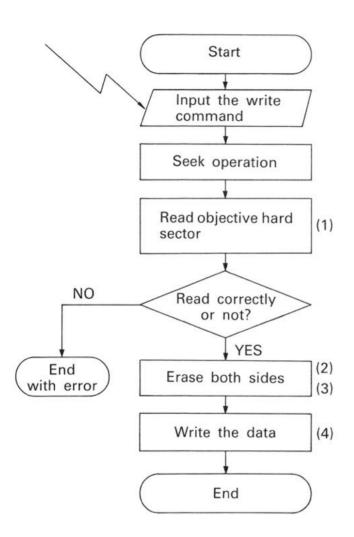

|     | 7-5. Write Operation                      | ;        | 39 |  |  |  |

|     | 7-6. Interface I/O operation ·····        | ,        | 40 |  |  |  |

|     | 7-7. Power-down and Low Battery Operation | /        | 43 |  |  |  |

|     | 7-8. DC Motor Drive Operation             |          |    |  |  |  |

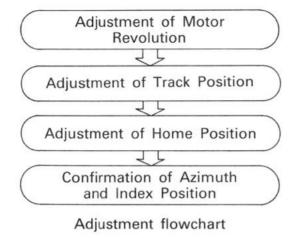

| 8.  | STANDARD MAINTENANCE                      | /        | 45 |  |  |  |

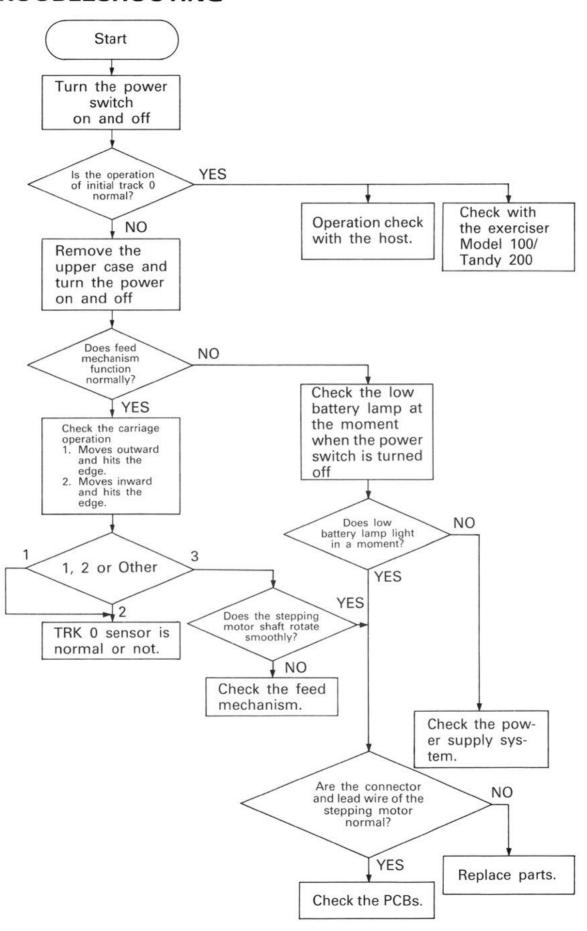

| 9.  | TROUBLESHOOTING                           | !        | 50 |  |  |  |

| 10. | P.C. BOARD VIEWS                          | إ        | 51 |  |  |  |

| 11. | EXPLODED VIEWS/PARTS LISTS                | !        | 55 |  |  |  |

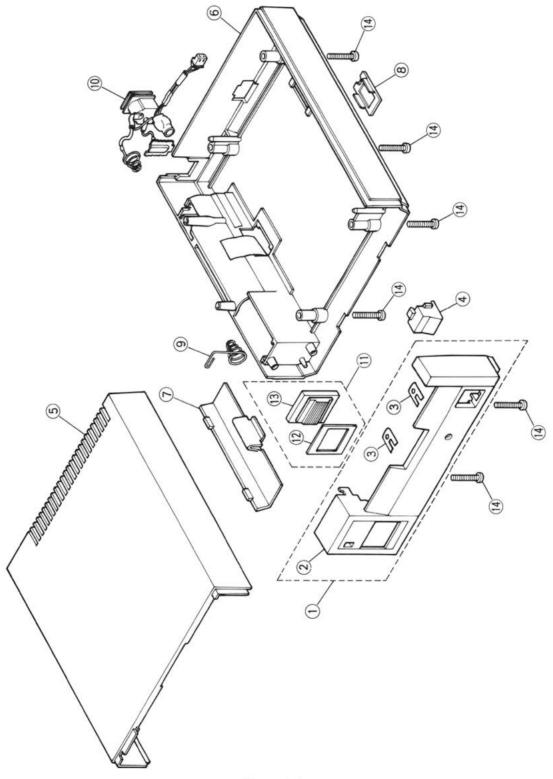

|     | 11-1. Housing Parts ·····                 | !        | 55 |  |  |  |

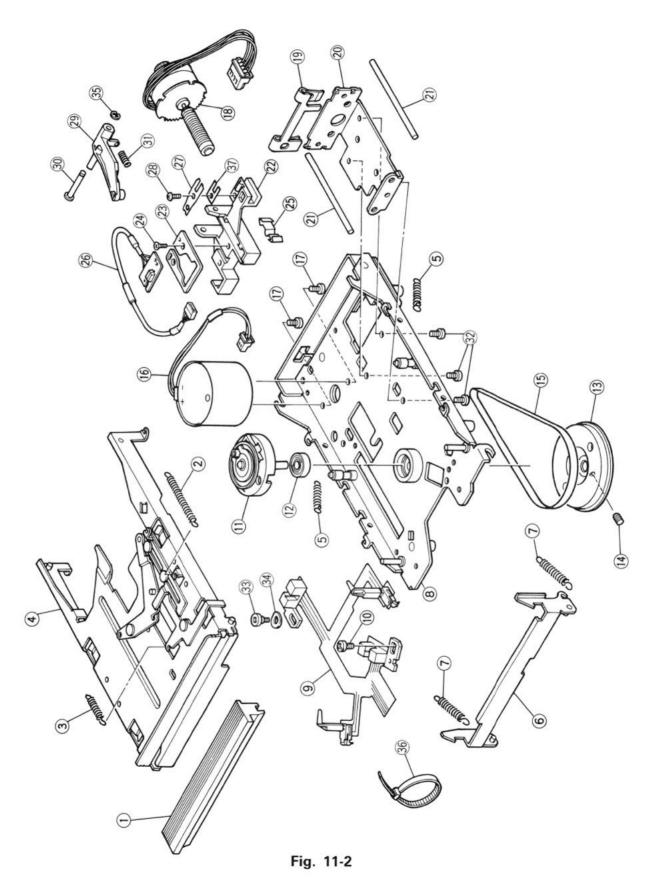

|     | 11-2. Drive Mechanism ·····               | إ        | 57 |  |  |  |

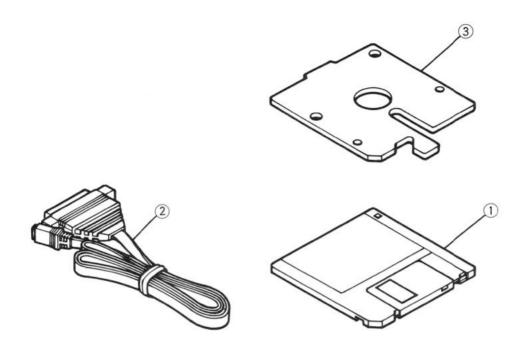

|     | 11-3. Accessories                         | !        | 59 |  |  |  |

|     | 11-4. Electronic/Electric Parts ·····     | (        | 60 |  |  |  |

| 12. | SOFTWARE SECTION                          |          | 70 |  |  |  |

|     | 12-1. Introduction of Software Section    |          |    |  |  |  |

|     | 12-2. Structure of Disk Data ·····        |          |    |  |  |  |

|     | 12-3. Internal Software Operation         |          |    |  |  |  |

|     | 12-4. Communication Reference ······      |          |    |  |  |  |

|     | 12-5. Appendices                          |          |    |  |  |  |

# 1. INTRODUCTION

The Tandy Portable Disk Drive 2 is a stand-alone 3.5-inch, microfloppy disk drive. It interfaces to the portable computer through the RS-232C port and may be powered by batteries for maximum portability.

Its compactness and light weight enable it to be carried along with the portable computer. Although tiny in size, a 3.5-inch diskette can store up to 200,000 bytes of data.

# 2. GENERAL SPECIFICATIONS

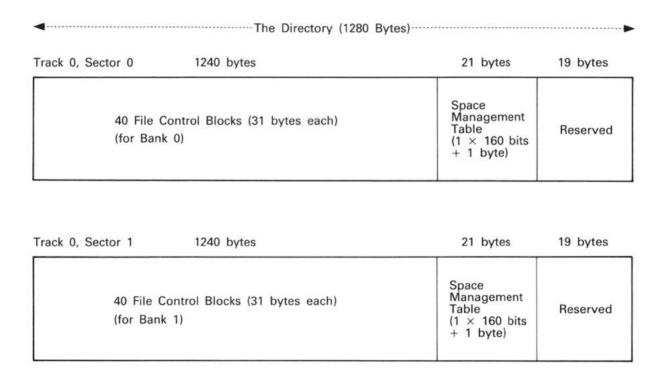

| 1.  | Storage capacity (Formatted) Per disk Per track Per hard sector                                     | 2,560 bytes                                                                                  |

|-----|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 2.  | Disk Number of surfaces Number of memory blocks Total number of tracks Total number of hard sectors | 1<br>160<br>80                                                                               |

| 3.  | Recording systems Recording method                                                                  | 4,064 BPI<br>135 TPI                                                                         |

| 4.  | Process time Average access time Track to track Settling time Motor start time                      | 40 ms<br>10 ms                                                                               |

| 5.  | Rotational speed                                                                                    | 300 rpm                                                                                      |

| 6.  | Number of Indexes                                                                                   | 2                                                                                            |

| 7.  | Power source                                                                                        | 4 AA Alkaline batteries<br>(Cat. No. 23-552) or<br>AC Adapter (26-3804)                      |

| 8.  | Power consumption Operating                                                                         | 0.08 W<br>Minimum 1.5 hours<br>Minimum 20 hours<br>4.1 V                                     |

| 9.  | Dimensions                                                                                          | $5-\frac{1}{4}$ " x $6-\frac{13}{32}$ " x $2-\frac{1}{8}$ "<br>133 (W) x 163 (L) x 54 (H) mm |

| 10. | Weight                                                                                              | 1 lb. 14 oz (850 grams)<br>(Including 4 batteries)                                           |

| 11. | Media used                                                                                          | Single-sided, 3.5-inch micro-<br>floppy disk                                                 |

| 12. | Interface  Transfer rate : Booting                                                                  | 9600 bits/sec.                                                                               |

# 3. DISASSEMBLY INSTRUCTIONS

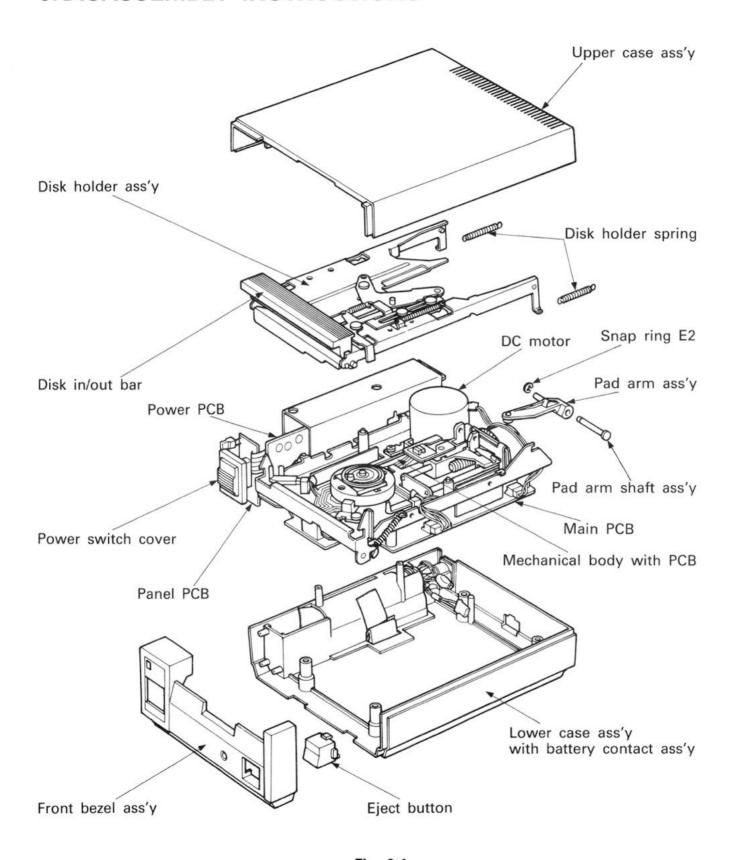

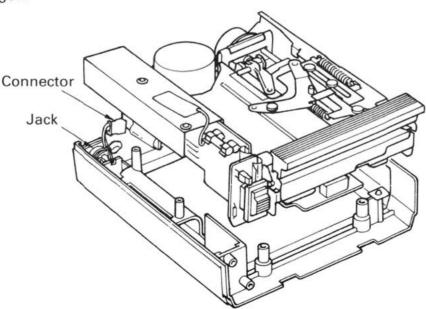

Fig. 3-1

# 3-1. Disassembly

#### Case

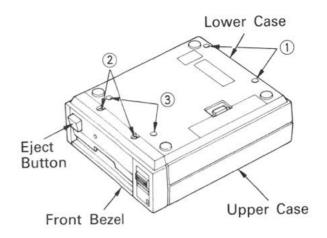

- 1. Refer to Fig. 3-2 and loosen the 2 set screws ① near the back of the lower case.

- 2. Remove the upper case.

- 3. Loosen the 2 set screws ② closest to the front edge of the lower case.

- 4. Remove the front bezel and the eject button.

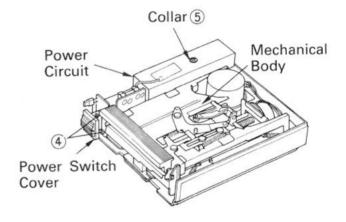

- Refer to Fig. 3-3 and remove the power switch cover.

- 6. Remove the 2 set screws 4.

- 7. Remove the set screw (5) and the collar.

- 8. Loosen the 2 set screws ③ near the front of the lower case. (See Fig. 3-2.)

- 9. Remove the connector that connects the jack and the power PCB (Fig. 3-4).

- Detach the lower case by holding onto the mechanical body and the power circuit (Fig. 3-3), then lift up.

Note: If the case is detached by holding onto only the mechanical body, the cable connecting the main PCB and the power PCB is likely to be damaged.

Fig. 3-2

Fig. 3-3

Fig. 3-4

## **PCB**

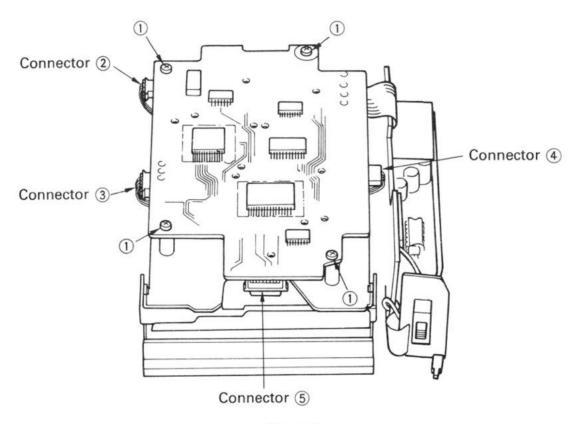

- 1. Refer to Fig. 3-5 and disconnect the 3 connectors 2, 3, and 4.

- 2. Loosen and remove the 4 set screws 1.

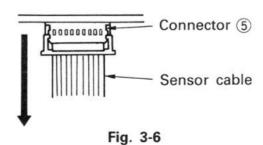

- 3. As shown in Fig. 3-6, remove the sensor cable after pulling off the outer part of the connector 5 in the direction of the arrow.

- 4. Remove the connector which connects the main PCB and the power PCB.

- 5. Remove the shielded plate.

- 6. The jumper lead wire which connects the Panel PCB to the power PCB is soldered. Detach the wire by removing the solder.

Fig. 3-5

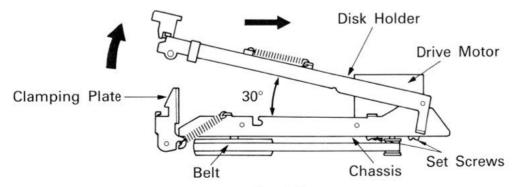

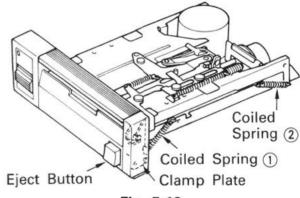

#### Disk Holder

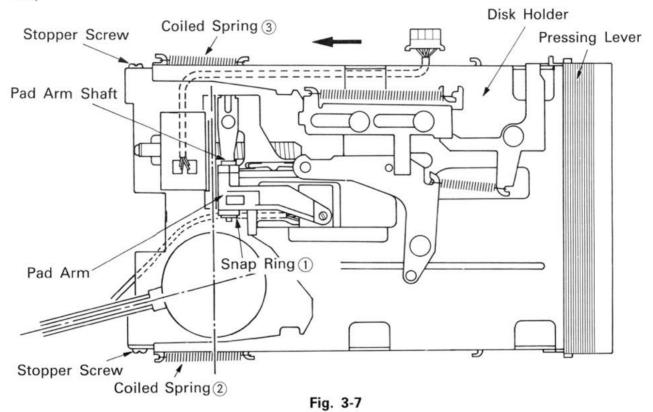

- 1. Remove the snap ring ① and pull out the pad arm shaft (Fig. 3-7).

- 2. Remove the pad arm. The pad-pressing coiled spring under the pad arm will be automatically removed with the pad arm.

- 3. Remove the 2 coiled springs 2 and 3.

- 4. Remove the 2 stopper screws.

- 5. Release the lock of the clamping plate and remove the disk holder by pulling it backward while holding it up at about a 30-degree angle (between the chassis and the disk holder). (Fig. 3-8)

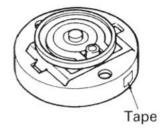

## **Drive Motor**

- 1. Remove the belt.

- 2. Remove the drive motor by loosening the 2 set screws.

Fig. 3-8

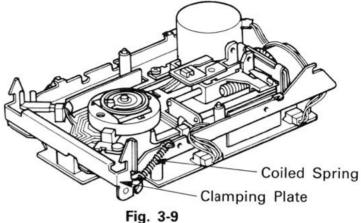

## Clamping Plate

- Remove the 2 coiled springs on both sides of the rear portion of the unit.

- 2. Remove the clamping plate.

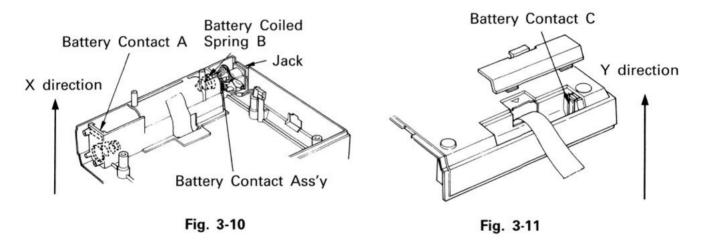

# **Battery Contact**

- 1. Remove the battery cover on the rear side of the lower case.

- 2. Move battery contact A in the X direction for removal (Fig. 3-10).

- 3. Move the jack and battery coiled spring B in the X direction for removal.

- 4. Remove battery contact C by moving it in the Y direction from the rear side of the lower case (Fig. 3-11).

# 3-2. Reassembly

Parts are reassembled in the reverse order of disassembly. The following items require additional explanation.

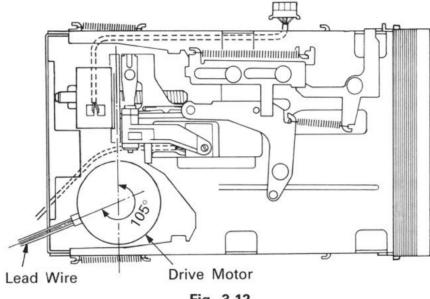

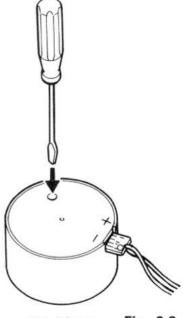

#### **Drive Motor**

When reassembling the drive motor, be sure that the lead wire is positioned at a 105° angle as shown in Fig. 3-12.

Fig. 3-12

#### IMPORTANT:

· Shielded Wire of the Head

Position the shielded wire so that it will not stretch when the head is moved to the center, and so that it will not apply excessive force to the head when the head is moved to the outermost periphery (or the position of Track 0).

#### Case

Do not let the legs (a) of the upper case interfere with the movement of the shielded wire of the head (Fig. 3-13). Also, be sure to provide sufficient length to the shielded wire so that it can move freely, even if the head is moved to the center.

Fig. 3-13

# 4. BLOCK DIAGRAM

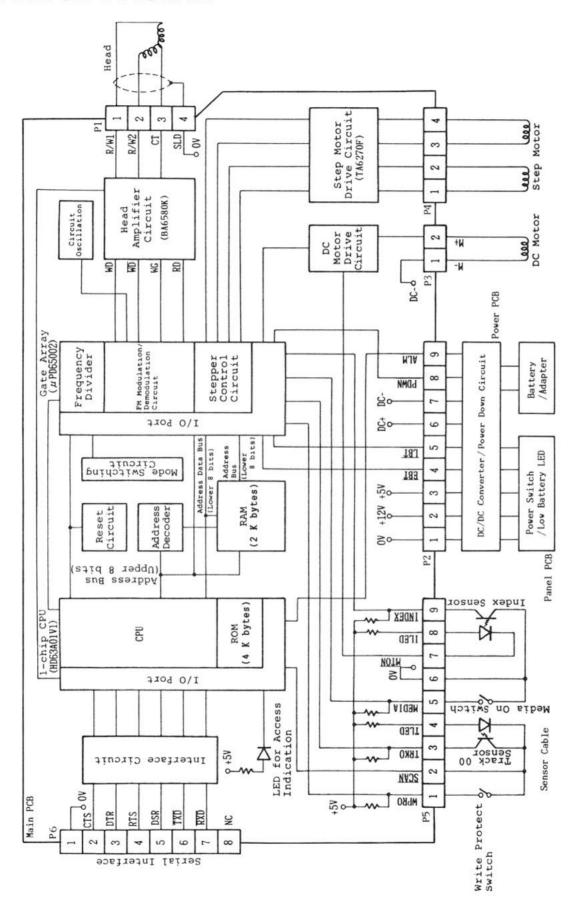

Fig. 4-1

# 5. PRINCIPLES OF MECHANICAL OPERATION

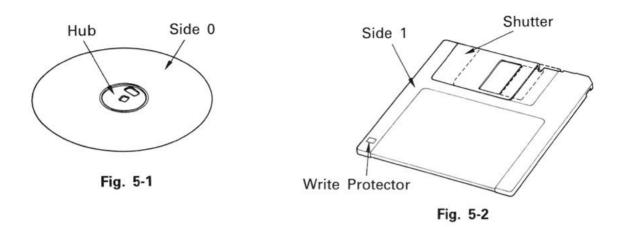

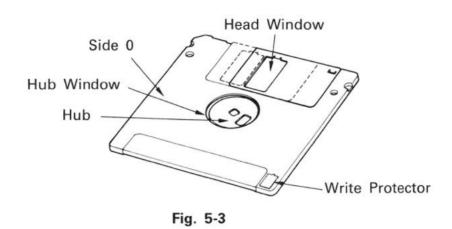

# 5-1. Structure of Disk

The disk has a magnetic sheet (Fig. 5-1) protected by 2 hard plastic cases (Figs. 5-2 and 5-3). The read/write operation is performed when the shutter slides open and the head comes in contact with the disk at the head window.

# 5-2. Disk Driving Mechanism

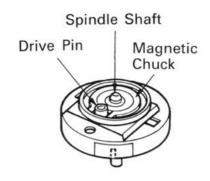

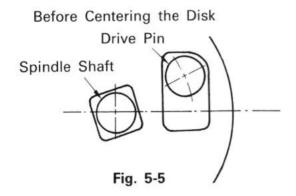

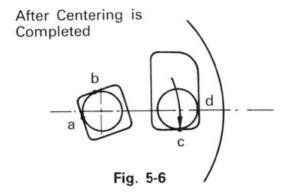

The hub is made of magnetic metal and provided with 2 holes as shown in Fig. 5-3. The spindle shaft goes into the center hole and the drive pin into the adjacent hole (Fig. 5-4). When the disk is inserted into the disk drive, the hub is attracted by the magnetic chuck. The spindle rotates clockwise and the drive pin moves into the positions shown in Figs. 5-5 and 5-6. When the disk is correctly centered, the spindle shaft touches the edge of the square hole at points a and b (Fig. 5-6) and the drive pin touches the edge of the longer hole at points c and d. Thus, unwanted side-to-side motion is prevented, even though the spindle rotates at 300 rpm.

Fig. 5-4

# 5-3. Head Positioning Mechanism

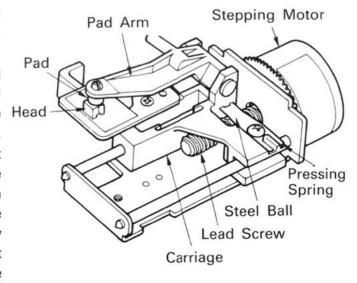

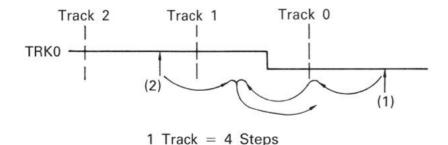

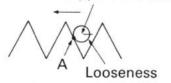

The head attached to the carriage is positioned by the stepping motor and the lead screw. When the stepping motor is supplied with 1 pulse, the lead screw rotates 15° and the head moves 0.046875 mm with the aid of a steel ball. The head moves 1 track (0.1875 mm) Head when the stepping motor receives 4 pulses. The Portable Disk Drive 2 is designed so that the head always moves outward for more accurate positioning. To move the head from Tr0 to Tr1, 6 pulses are actually required. The head advances from Tr0 by 5 pulses, thereby moving beyond Tr1 by 1 pulse, and then it returns to Tr1 by 1 additional pulse for more accurate positioning.

Fig. 5-7

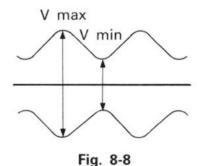

## 5-4. Structure of Read/Write Head

The read/write head is always in contact with the disk by means of a head pad. The surface of the head is designed so that the wear of the head and the disk are at a minimum and that the signal for reading data from the disk is at a maximum.

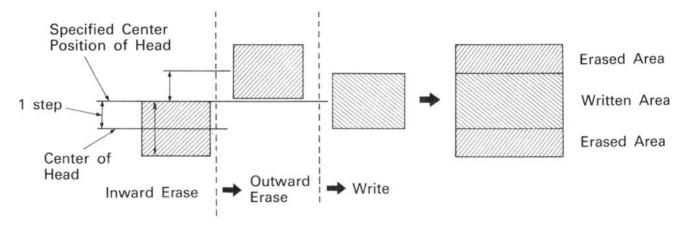

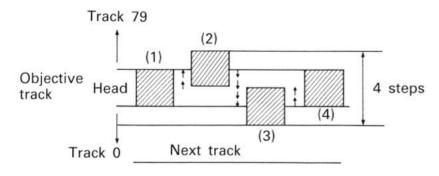

The Portable Disk Drive 2 has a single gap head without an erase gap; the read, write and erase operations are all performed by 1 coil (Fig. 5-8). The head moves 1 pulse inward (0.046875mm) and 2 pulses outward to erase; then it moves 1 pulse inward to write the data (Fig. 5-9). Therefore, it is possible to read the data even if tracking is off, because the data area is located between the erased areas.

Fig. 5-8

Fig. 5-9

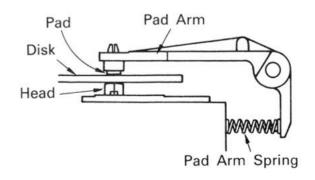

## 5-5. Pad Mechanism

The read/write head comes into contact with the disk while the head pad pushes the disk from the upper side. The material and shape of the pad, and the strength of the pad arm spring, are designed so that the head receives the most adequate signal from the disk during the read/write operation.

Fig. 5-10

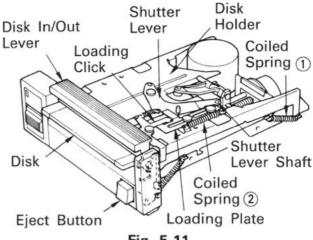

# 5-6. Disk Eject Mechanism

When the disk is entirely inserted into the holder, the loading click and loading plate are engaged and locked. When the disk in/out lever is pushed downward, the clamp plate and cylindrical convex part of the disk holder are engaged and locked.

When the eject button is pressed, the clamp plate is released from the cylindrical convex part of the disk holder and the loading click is released from the loading plate.

Then the disk holder is raised by the coiled spring 1 and the disk is pushed out by the loading plate connected to another coiled spring (2).

This is how the disk is ejected.

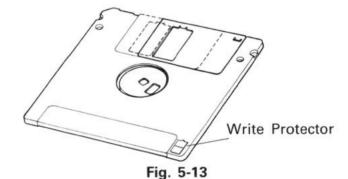

#### 5-7. Write Protector

The disk is provided with the sliding-type write protector (Fig. 5-13).

When this shutter slides open, the disk is in a state of write protection. The Portable Disk Drive 2 detects this window with the writeprotect detection switch.

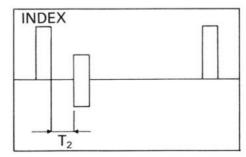

#### 5-8. Index

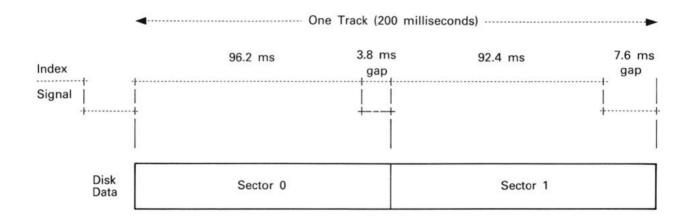

The disk drive requires an index signal for read/write operations.

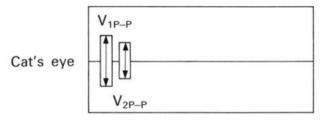

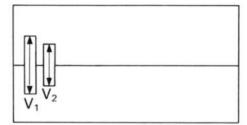

To detect the index signal, an index sensor searches for a big notch and a small one provided on the side face of the encoder (Fig. 5-14).

#### 5-9. Disk Detection

When the disk is inserted and locked into regular position, the disk detection switch is pressed by the disk.

This switch detects whether or not a disk is in the disk drive.

Fig. 5-11

Fig. 5-12

Write-Protect **Detection Switch** Encoder Notch Disk Detection Index Sensor Switch Fig. 5-14

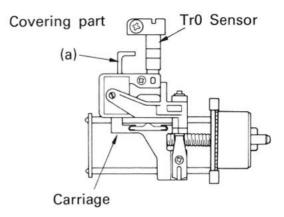

# 5-10. Home Position Return

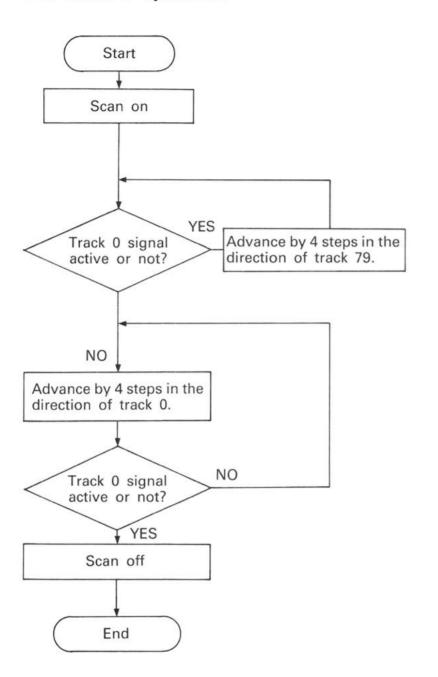

When the disk drive is supplied with power, the carriage returns to Tr0 (track 0).

When the carriage moves to the right and the covering part (a) in Fig. 5-15 covers the slit of the Tr0 sensor, the read/write head is positioned at Tr0.

Fig. 5-15

# 6. PRINCIPLES OF ELECTRONIC OPERATION

# 6-1. Electronic Components

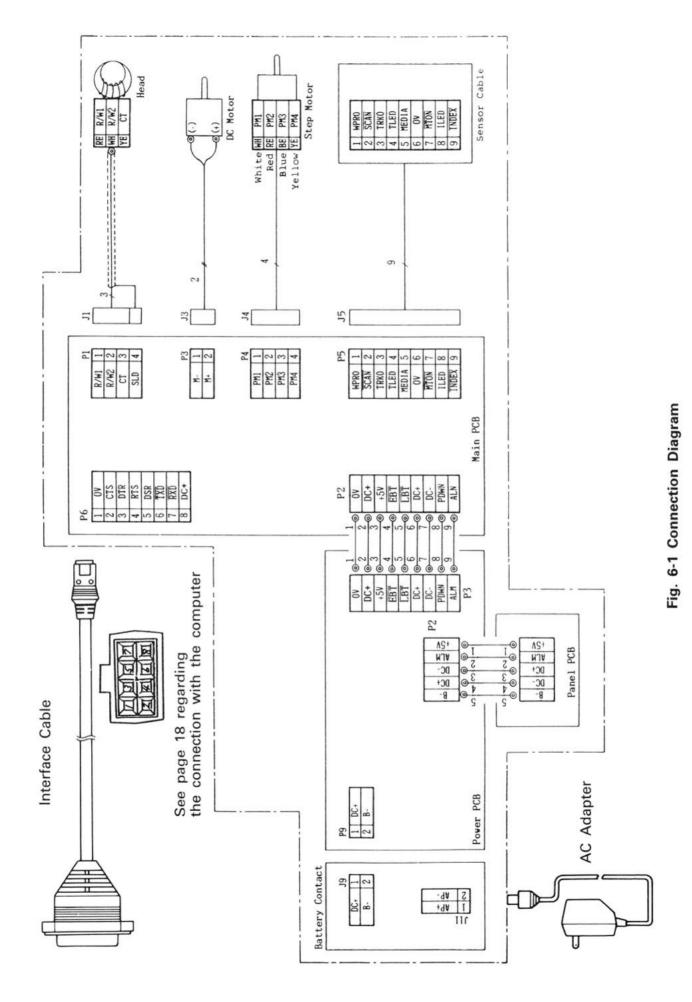

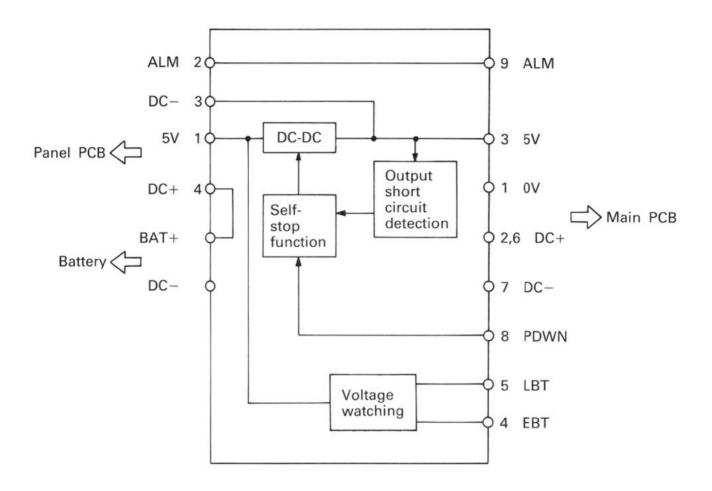

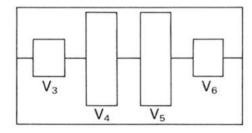

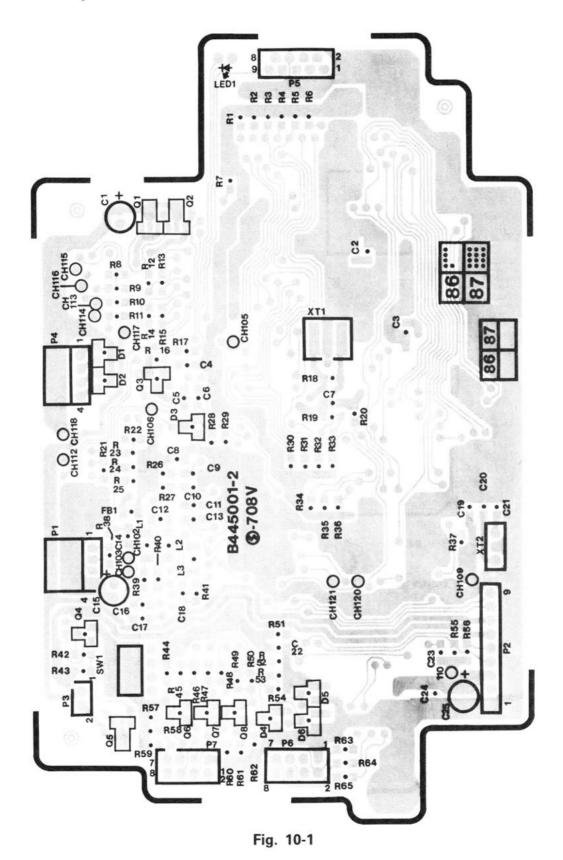

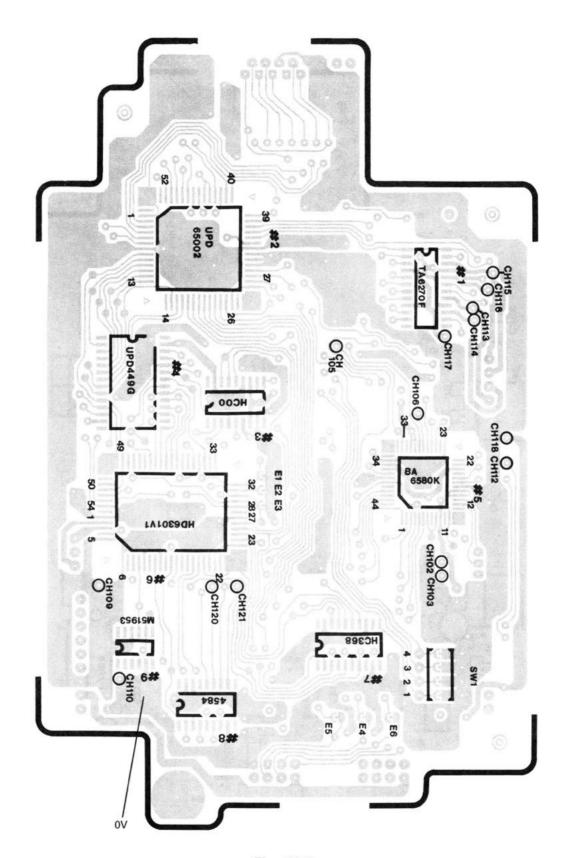

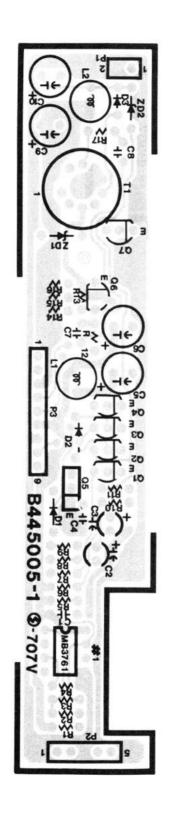

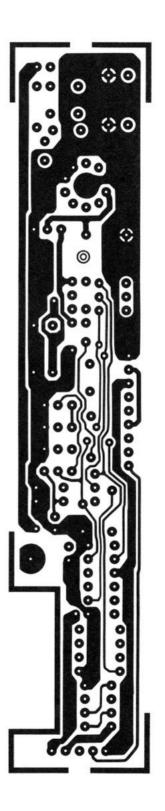

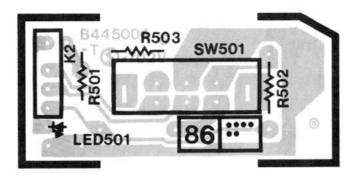

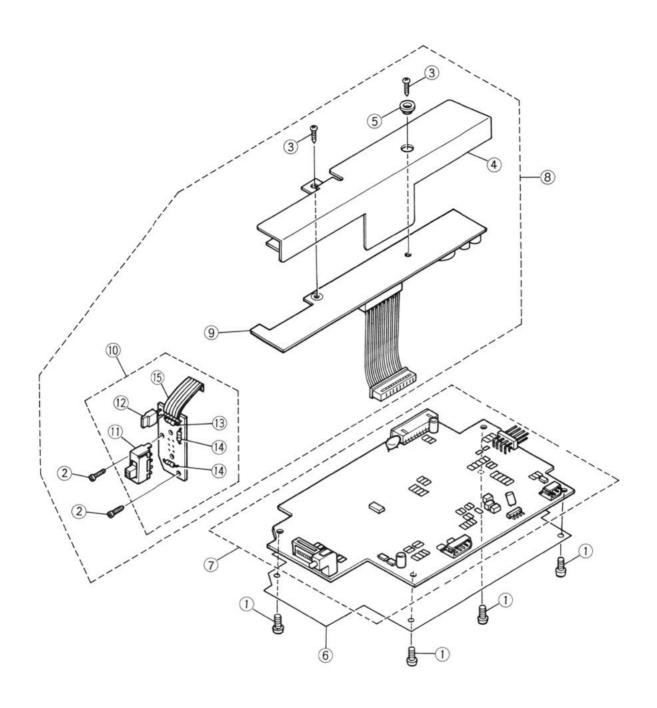

The electronic section consists of 3 PCBs (printed circuit boards) (See Fig. 6-1.):

- Main PCB

- Panel PCB

- Power PCB

The Panel PCB has a flat cable which connects with the Power PCB.

- 16 -

# 6-2. Main PCB

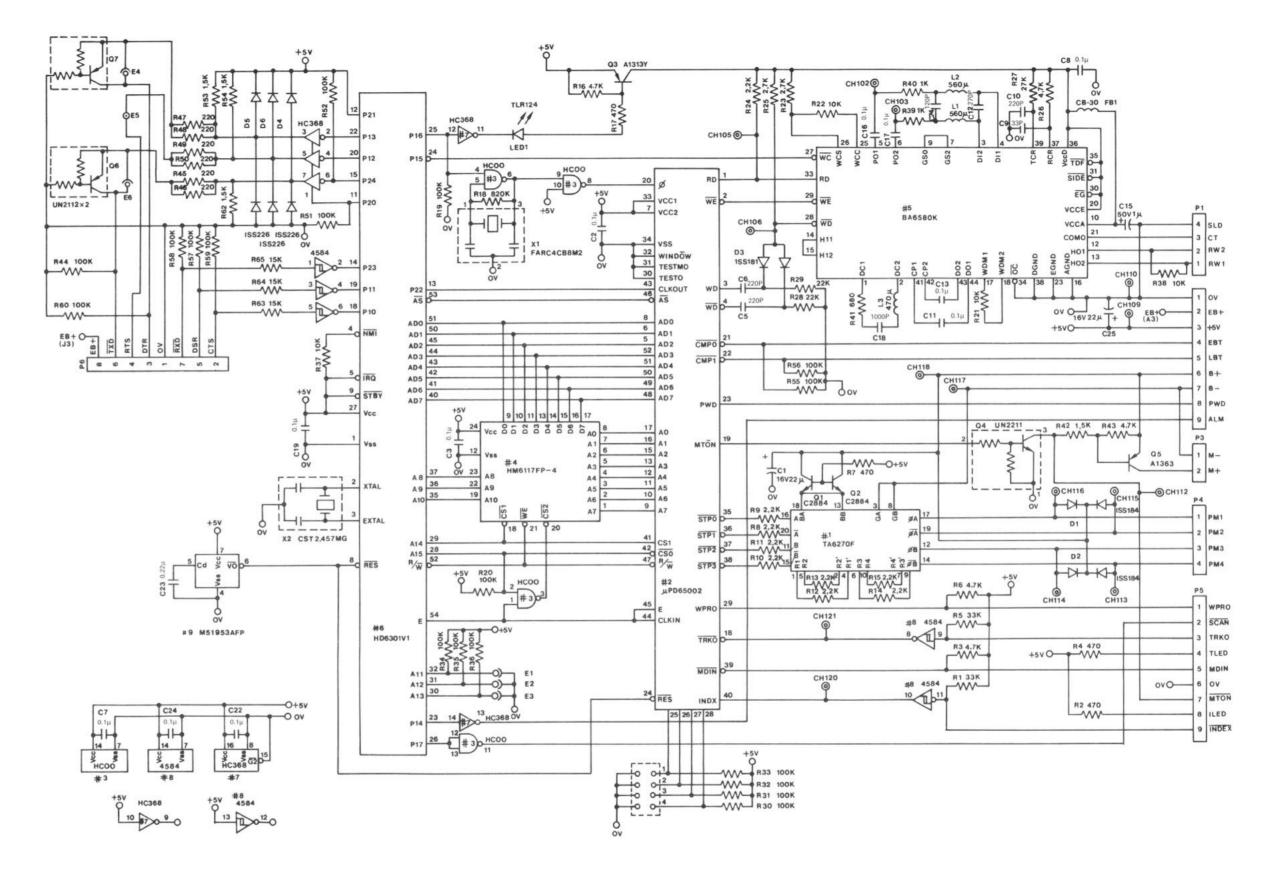

The main PCB controls the entire system and consists of an interface circuit, 1-chip CPU, gate array, read/write amplifier, step motor driver, RAM, oscillation circuit, reset circuit and address decoder.

#### 6-2-1. Interface Circuit

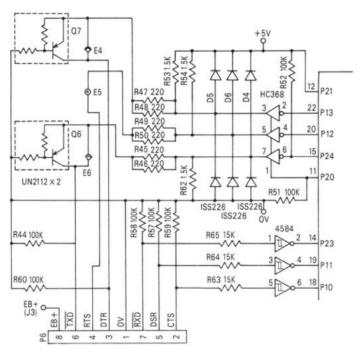

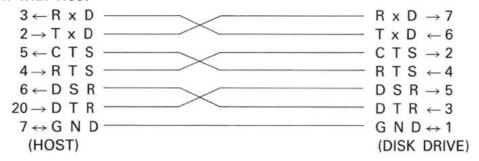

Fig. 6-2. is an input and output circuit which shows the connection with a host (for example, a Model 100) by a pseudo RS-232C interface. (See the schematic diagram of the main PCB in Fig. 12-1 on page 67.)

Fig. 6-2

R45 to R50 are protective resistors for output short.

D4 to D6 are diodes to protect the IC (HC368) from latch-up.

R63 to R65 are protective resistors; the input voltage can be used with a variation of up to  $\pm 12$ V. Q6 and Q7 are signal level converters for the Model 100 and/or Tandy 200 interface circuit. R53 and R54 are pull-up resistors.

R57 to R59 and R62 are pull-down resistors.

#### **Electrical Characteristics**

The sequence of the signal conforms to RS-232C.

# Connection with Host

# Communication Method

Half-Duplex, Start-Stop Synchronization (See pages 39~41 for details.)

1 Start Bit, 8-Bit Data, 1 Stop Bit without Parity

Transfer Rate

Operating 1200, 4800, 9600, 19200 bps

## 6-2-2. One-Chip CPU (HD6301V1)

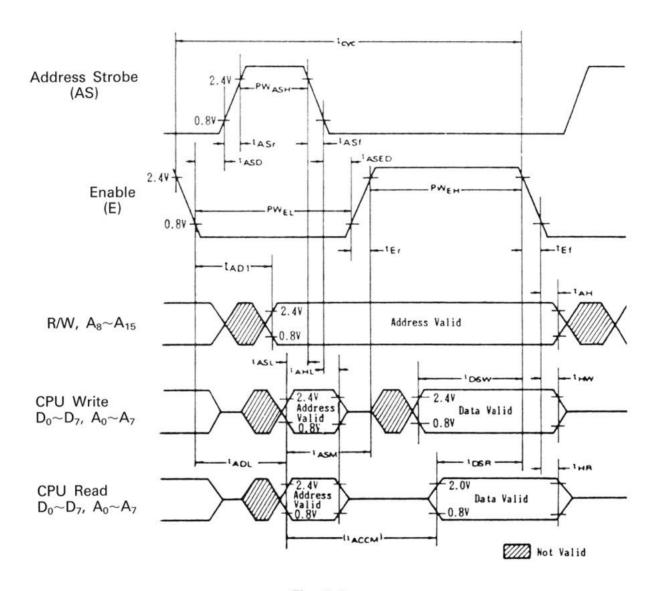

This 8-bit central processing unit (CPU) controlling the system of the disk drive has one serial interface, several I/O ports, 4K bytes of mask programmed ROM, and 128K bytes of RAM. The functions of each terminal will be described later. This CPU functions at mode 6. The 8 bits of data and the lower 8 bits of address lines are multiplexed. Fig. 6-3 shows the bus timing. The lower byte of the address is determined at the falling edge of AS. The read/write operations of the data are performed at the falling edge of E. This IC is made by the CMOS process, so that it consumes less power.

Fig. 6-3

Terminal and Function CPU (HD6301V1)

| Terminal | Pin No. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NMI      | 4       | Non-maskable interrupt input. This unit does not use this terminal. Always high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ĪRQ      | 5       | Interrupt input. This unit does not use this terminal. Always high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND      | 1       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTAL     | 2       | Clock input for CPU. Oscillation is generated by the ceramic resonator of 2.457MHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| EXTAL    | 3       | Clock input for CPU. This is also used with the oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|          |         | XTAL EXTAL TO THE PROPERTY OF |

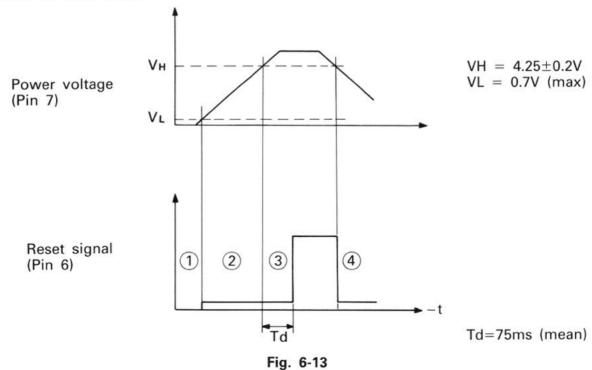

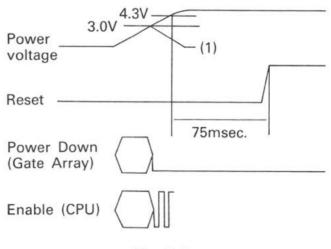

| RES      | 8       | Reset input. The low level is held for 20msec. or more after the unit is powered on, then changes to the high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| STBY     | 9       | Stand-by input terminal. This terminal is not used. Always high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| P20      | 11      | When resetting, this port works as a mode setting input port. During this time its level is set to low. When the CPU is operating, this port works for serial interface control.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| P21      | 12      | Input port to set the mode of the CPU. Always high level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P22      | 13      | When resetting, this input port sets the mode of CPU. After resetting, it is the input port for the standard clock of the serial interface (8 times the baud rate). Duty of the standard clock: 50%. The timing is as follows:  RES P22 Min. 50µsec.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Terminal      | Pin No.                                       | Function                                                                                                                                                                                                                                                                                                                                                         |

|---------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P23<br>(RxD)  | 14                                            | Input port to receive the data of the serial interface. High level when there is no communication with the host.                                                                                                                                                                                                                                                 |

| P24<br>(TxD)  | 15                                            | Output port to transmit the data of the serial interface. High level when there is no communication with the host.                                                                                                                                                                                                                                               |

| P10<br>(CTS)  | 18                                            | Input port to receive the request to send signal which is the interface control signal from the host.                                                                                                                                                                                                                                                            |

| P11 (DSR)     | 19                                            | Input port to receive the data terminal ready signal from the host.                                                                                                                                                                                                                                                                                              |

| P12           | 20                                            | Output port to permit the transmission to the host.                                                                                                                                                                                                                                                                                                              |

| P13<br>(DTR)  | 22                                            | Output port to indicate this unit is powered. Always high level after the power is supplied.                                                                                                                                                                                                                                                                     |

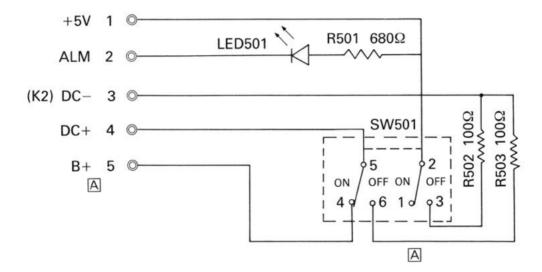

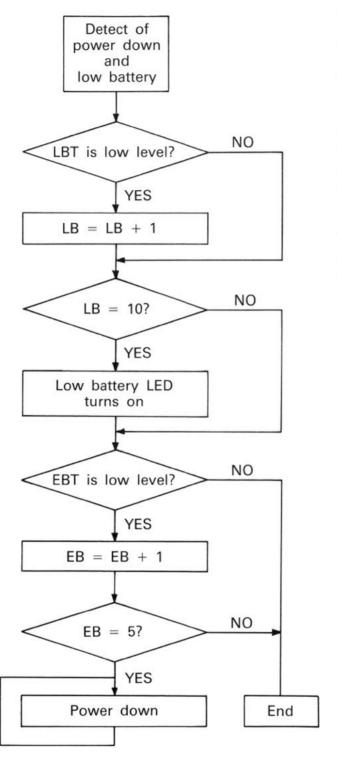

| P14<br>(ALM)  | 23                                            | When the LBT (low battery) signal from the power PCB is high level, the CPU recognizes the low battery state and sets this terminal to high level to light the low battery LED. The CPU detects the LBT signal only while the serial interface is awaiting input or during input. This signal is not detected during the seeking, reading or writing operations. |

| P15<br>(WC)   | 24                                            | Output port to control head write current. When the read/write head is located from track 0 to track 59, its level is low; and when it is located from track 60 to track 79, its level is high.                                                                                                                                                                  |

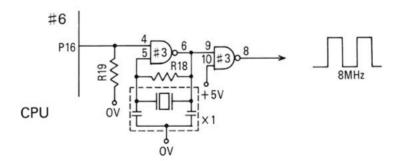

| P16           | 25                                            | The output is low level when reading or writing from/to the disk. The CPU shuts down the reading or writing circuit to save power while the output is high level.  This port also controls access indicator LED and clock oscillator for modulation and demodulation.                                                                                            |

| P17<br>(SCAN) | 26                                            | The output is high only when detecting the track 0 (zero) signal and the write-protect signal. During low levels, the track 0 sensor and the write-protect switch are not supplied with electricity to save power.                                                                                                                                               |

| Vcc           | 27                                            | +5V of the power supply.                                                                                                                                                                                                                                                                                                                                         |

|               | 6,7,10,16,<br>17,21,33,<br>34,38,39,<br>46~49 | These pins are non-connected.                                                                                                                                                                                                                                                                                                                                    |

| Terminal | Pin No. | Function                                                                                                                                                                                                             |

|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A15      | 28      | A14, A15 of the address bus.                                                                                                                                                                                         |

| A14      | 29      |                                                                                                                                                                                                                      |

| A13      | 30      | Mode setting input ports for CPU operation.                                                                                                                                                                          |

| A12      | 31      |                                                                                                                                                                                                                      |

| A11      | 32      |                                                                                                                                                                                                                      |

| A10      | 35      | A10, A9, A8 of the address bus.                                                                                                                                                                                      |

| A9       | 36      |                                                                                                                                                                                                                      |

| A8       | 37      |                                                                                                                                                                                                                      |

| AD7      | 40      | The lower 8 address bits and the 8 data bits are multiplexed.                                                                                                                                                        |

| AD6      | 41      |                                                                                                                                                                                                                      |

| AD5      | 42      |                                                                                                                                                                                                                      |

| AD4      | 43      |                                                                                                                                                                                                                      |

| AD3      | 44      |                                                                                                                                                                                                                      |

| AD2      | 45      |                                                                                                                                                                                                                      |

| AD1      | 50      |                                                                                                                                                                                                                      |

| AD0      | 51      |                                                                                                                                                                                                                      |

| R/W      | 52      | The read/write signal of the CPU. The low level is output in writing and the high level in reading. The high level is also output during reset.                                                                      |

| ĀS       | 53      | Strobe signal output to separate the address bus from the address/ data bus.                                                                                                                                         |

| E        | 54      | Output of system clock. The frequency of 2.45MHz is divided by one fourth. The RAM and the gate array are accessed when this clock is high. The data is read/written from/to them at the falling edge of this clock. |

# 6-2-3. Gate Array (µPD65002G)

The gate array of 857 gates is made through the CMOS process. It consists of the input port, the output port, the dividing circuit, the FM/MFM modulation/demodulation circuit, and the address (lower 8 bits)/data separating circuit. Refer to the following table for the functions of each terminal of the gate array.

Gate Array (µPD65002) Terminals and Functions

| Terminal | Pin No. | Function                                                                                                                                                                                                                                                                                                      |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RD       | 1       | Modulated signal input which is read out of the disk. Pulse width: 250µsec. Pulse interval: approx. 4µsec. or 8µsec.                                                                                                                                                                                          |

| WE       | 2       | Low level output when writing to the disk. The writing circuit functions when $\overline{\text{WE}} = \text{low}.$                                                                                                                                                                                            |

| WD       | 3       | Modulated data output for writing to the disk. The $\overline{\text{WD}}$ is an inverted                                                                                                                                                                                                                      |

| WD       | 4       | signal of the WD and vice versa. The width of the high and low levels is 4µsec. or 8µsec. during writing. And the level is fixed at high or low during erasing.                                                                                                                                               |

| AD0      | 8       | Address (lower 8 bits)/data bus. Used to input or output the                                                                                                                                                                                                                                                  |

| AD1      | 6       | multiplexed signals.                                                                                                                                                                                                                                                                                          |

| AD2      | 5       |                                                                                                                                                                                                                                                                                                               |

| AD3      | 52      |                                                                                                                                                                                                                                                                                                               |

| AD4      | 51      |                                                                                                                                                                                                                                                                                                               |

| AD5      | 50      |                                                                                                                                                                                                                                                                                                               |

| AD6      | 49      |                                                                                                                                                                                                                                                                                                               |

| AD7      | 48      |                                                                                                                                                                                                                                                                                                               |

| Vcc1     | 33      | +5V power supply.                                                                                                                                                                                                                                                                                             |

| Vcc2     | 7       |                                                                                                                                                                                                                                                                                                               |

| A7       | 9       | Address bus (lower 8 bits). The AD0-AD7 are latched by the AS as                                                                                                                                                                                                                                              |

| A6       | 10      | address signal. A0 and A1 are used as signals to select the internal register.                                                                                                                                                                                                                                |

| A5       | 11      | Togister.                                                                                                                                                                                                                                                                                                     |

| A4       | 12      |                                                                                                                                                                                                                                                                                                               |

| А3       | 13      |                                                                                                                                                                                                                                                                                                               |

| A2       | 15      |                                                                                                                                                                                                                                                                                                               |

| A1       | 16      |                                                                                                                                                                                                                                                                                                               |

| A0       | 17      |                                                                                                                                                                                                                                                                                                               |

| TRK0     | 18      | To input the low level when the head is at track 0. Therefore, this signal changes from high to low while the head moves from track 1 to 0. This signal is valid, however, only when the SCAN signal is active (CPU P17 is high level) because the sensor circuit is not supplied with power when SCAN = Low. |

| Terminal | Pin No. | Function                                                                                                                                                                                                                                                     |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MTON     | 19      | The DC motor rotates when a high level signal is output. The index signal is valid only when this signal is high. The index sensor stops to save power during low levels.                                                                                    |

| φ        | 20      | Standard clock input of 8 MHz.                                                                                                                                                                                                                               |

| COMP0    | 21      | The low level is input when the battery voltage drops to 3.5V or less. When this signal is input, the PWD outputs the high level to turn off the power.                                                                                                      |

| COMP1    | 22      | The low level is input when the battery voltage drops to 4.1V or less. When this signal is input, battery replacement is required. P15 of the CPU changes to the low level to indicate low battery status.                                                   |

| PD       | 23      | Usually low level after power is supplied. If the power voltage is insufficient, the low level signal is input from COMP0 and PWD outputs the high level to turn off power.                                                                                  |

| RES      | 24      | The reset signal input. A low level input makes all functions return to their states: CL OUT = high, PWD = low, $\overline{WE}$ = high, and $\overline{STEP0}$ - $\overline{STEP3}$ = high, RES goes high level 20msec. or more after the power is supplied. |

| SCLK0    | 25      | SCLK0, SCLK1, SCLK2 and SCLK3 are input ports that determine                                                                                                                                                                                                 |

| SCLK1    | 26      | drive interface mode. In connecting Portable Disk Drive 2 with Model 100/102, Tandy 200,                                                                                                                                                                     |

| SCLK2    | 27      | these pins are pulled up to +5V.                                                                                                                                                                                                                             |

| SCLK3    | 28      |                                                                                                                                                                                                                                                              |

| Terminal | Pin No. | Function                                                                                                                                                                                                                                                                       |

|----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WPRO     | 29      | Write-protect signal input. A high level signal creates a write-protect state. Valid only when the SCAN is high since the switch is not supplied with power when SCAN is low.                                                                                                  |

| TESTM0   | 30      | Input terminal to check the gate array by manufacturer. Direct                                                                                                                                                                                                                 |

| TEST0    | 31      | connection with the ground.                                                                                                                                                                                                                                                    |

| WINDOW   | 32      | Window signal input terminal for MFM demodulation. Direct connection with the ground because of FM modulation.                                                                                                                                                                 |

| GND      | 34      | Ground                                                                                                                                                                                                                                                                         |

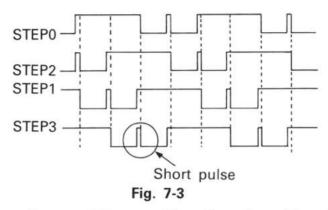

| STEP0    | 35      | Output for the excitation of the step motor. Phase excitation is                                                                                                                                                                                                               |

| STEP1    | 36      | possible when STP0 and STP2 are in an inverted relationship with                                                                                                                                                                                                               |

| STEP2    | 37      | STP1 and STP3, respectively. Refer to the software manual for details on the output stage.                                                                                                                                                                                     |

| STEP3    | 38      |                                                                                                                                                                                                                                                                                |

| MDIN     | 39      | Signal input detects whether the disk is set in the unit. A low level indicates the loading of the disk. The unloading of the disk (the rise of the signal) is detected by the D-FF. The change of the disk is also detected. Detection is performed by the mechanical switch. |

| INDX     | 40      | Index signal input. Two types of pulses, a long one and a short one, input per one rotation of disk. Pulse length: approx. 6msec. and 3msec.                                                                                                                                   |

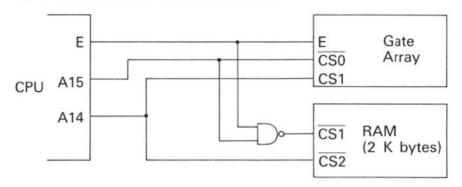

| CS0      | 42      | Signal input to select the register of the gate array.  Signal input to select the register of the gate array.                                                                                                                                                                 |

| CS1      | 41      | level and CS1 is high for selection of the register.                                                                                                                                                                                                                           |

| CLKIN    | 44      | Standard clock input for the CLKOUT. The signal from CLKIN is divided by 2 <sup>n</sup> (where n is software selectable) and provided for CLKOUT.                                                                                                                              |

| CLKOUT   | 43      | Standard clock output for the serial interface. The mode of the CPU is set at the high level during reset.                                                                                                                                                                     |

| Е        | 45      | System clock input from the CPU. When this signal is high, the register is accessed.                                                                                                                                                                                           |

| AS       | 46      | Control signal input to separate the address (lower 8 bits) and the data bus.                                                                                                                                                                                                  |

| R/W      | 47      | Signal input to read and write in the register. High level in resetting.                                                                                                                                                                                                       |

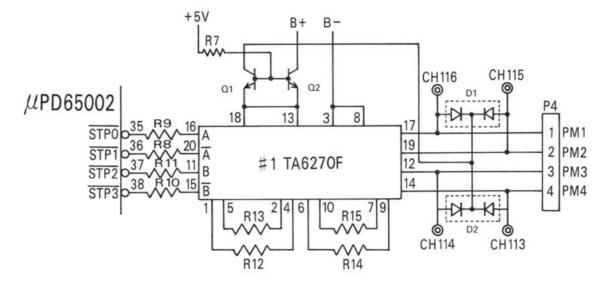

# 6-2-4. Step Motor Drive Circuit

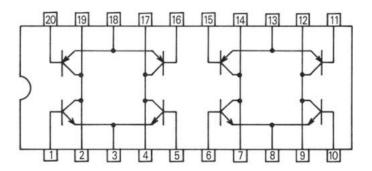

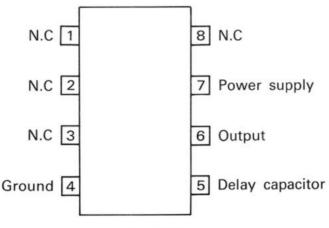

The step motor drive circuit is constituted as shown in Fig. 6-6.

R7, Q1 and Q2 cause the drive voltage of the step motor to drop from 5V to about 3.6V. TA6270F is a transistor array and its internal connection is shown in Fig. 6-7.

D1 and D2 absorb the spike which occurs when the excitation phase is changed.

Fig. 6-6

Fig. 6-7

# 6-2-5. Read/Write Amplifier Circuit IC (BA6580K)

| Signal                 | Pin No.     | Function                                                                                                                                                                           |

|------------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RW01<br>RW02           | 12<br>13    | SIDE0 Read/Write Head connection terminal.                                                                                                                                         |

| COM0                   | 21          | SIDE0 Read/Write Head common connection terminal.                                                                                                                                  |

| RW11                   | 14          | SIDE1 Read/Write Head connection terminal. (Portable Disk Drive 2 does not use it.)                                                                                                |

| RW12                   | 15          |                                                                                                                                                                                    |

| COM1                   | 19          | SIDE1 Read/Write Head common connection terminal. (Portable Disk Drive 2 does not use it.)                                                                                         |

| GS0<br>GS1<br>GS2      | 9<br>8<br>7 | Read pre-amplifier gain selection terminal. GS0–GS1 connection set a gain of 100. GS0–GS2 connection set a gain of 200. Portable Disk Drive 2 connects 7–9 and uses a gain of 200. |

| PRE OUT1<br>PRE OUT2   | 6<br>5      | Read pre-amplifier. Differential output terminal.                                                                                                                                  |

| DIFF IN1<br>DIFF IN2   | 3<br>4      | Derivative differential input terminal.                                                                                                                                            |

| DIFF<br>CONST1         | 2           | Derivative constant connection terminal.                                                                                                                                           |

| DIFF<br>CONST2         | 1           |                                                                                                                                                                                    |

| DIFF OUT1<br>DIFF OUT2 | 44<br>43    | Derivative differential output terminal.                                                                                                                                           |

| COMP IN1<br>COMP IN2   | 41<br>42    | Comparator differential input terminal.                                                                                                                                            |

| TDF COMP               | 40          | Connects the resistor to revise a time constant of the time domain filter circuit.                                                                                                 |

| TDF CR                 | 39          | Connects a C-R time constant for the time domain filter.                                                                                                                           |

| RDO CR                 | 37          | This terminal is connected with the C-R time constant for read-data pulse width.                                                                                                   |

| READ<br>DATA           | 33          | Read-data output signal. This signal level is TTL-compatible.                                                                                                                      |

| TDF CONT               | 35          | This input signal controls the time constant of the time domain filter. When this input signal is low, the time constant will be reduced.                                          |

| <u>OC</u>              | 34          | This input signal controls the read-data output (33) feature. When this input signal is low, read-data output is active.                                                           |

| Signal        | Pin No. | Function                                                                                                                                                         |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WC SET        | 26      | This terminal is connected with the resistor that determines the write current of the R/W head.                                                                  |

| WC COMP       | 25      | This terminal is connected with the resistor that revises the write current of the R/W head.                                                                     |

| WC CONT       | 27      | This input signal controls the write current of the R/W head.                                                                                                    |

| WC GATE       | 29      | When this terminal is low level, BA6580K operates as a write amplifier.                                                                                          |

| W DATA        | 28      | This terminal receives the write data signal.                                                                                                                    |

| WR DUMP       | 17      | These terminals are connected with the write dumping resistor.                                                                                                   |

|               | 18      |                                                                                                                                                                  |

| E GATE        | 30      | When this terminal is low level, the erase gate will open. (Not used.)                                                                                           |

| EO 0          | 24      | Erase current sink terminal for SIDE0 of the R/W head. (Not used.)                                                                                               |

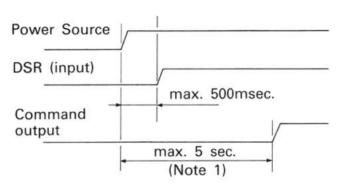

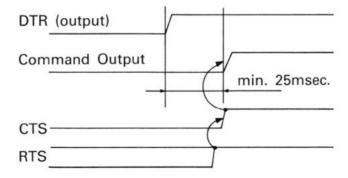

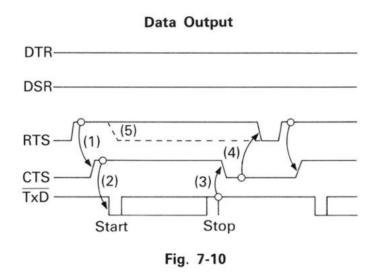

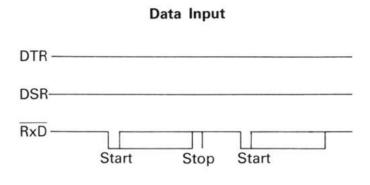

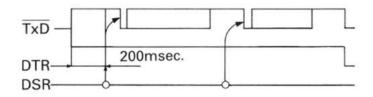

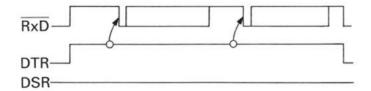

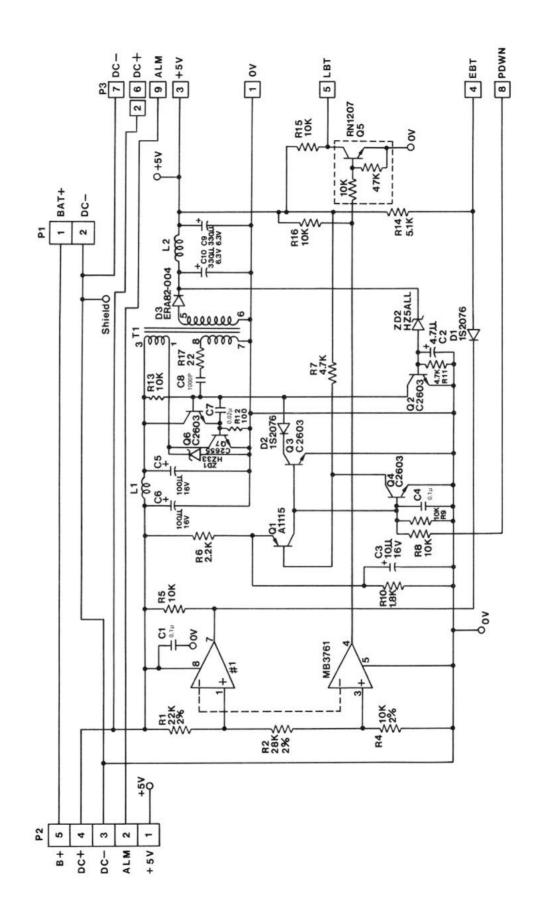

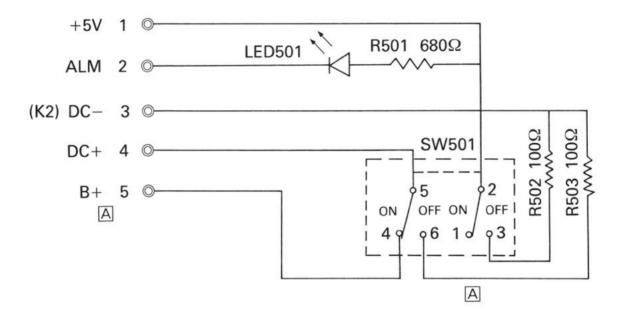

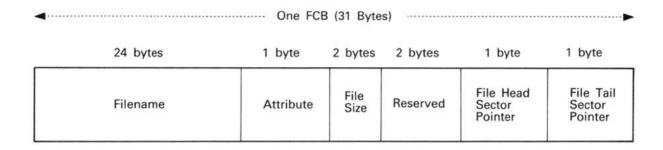

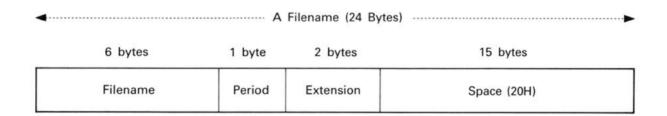

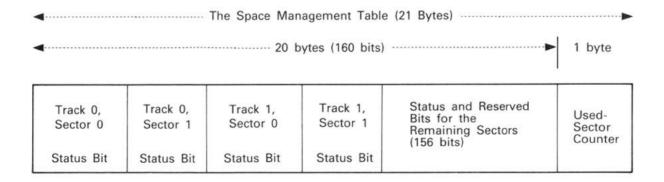

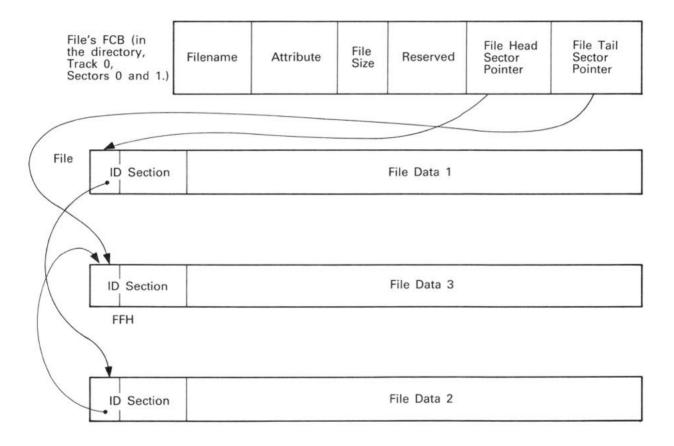

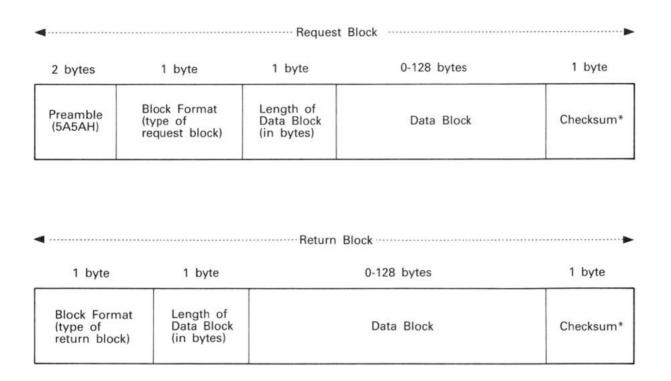

| EO 1          | 25      | Erase current sink terminal for SIDE1 of the R/W head. (Not used.)                                                                                               |